October 24, 2008

### LP38690-ADJ/LP38692-ADJ 1A Low Dropout CMOS Linear Regulators with Adjustable Output Stable with Ceramic Output Capacitors

# General Description

The LP38690/2-ADJ low dropout CMOS linear regulators provide 2.5% precision reference voltage, extremely low dropout voltage (450mV @ 1A load current,  $V_{OUT} = 5V$ ) and excellent AC performance utilizing ultra low ESR ceramic output capacitors.

The low thermal resistance of the LLP and SOT-223 packages allow the full operating current to be used even in high ambient temperature environments.

The use of a PMOS power transistor means that no DC base drive current is required to bias it allowing ground pin current to remain below  $100 \ \mu$ A regardless of load current, input voltage, or operating temperature.

Dropout Voltage: 450 mV (typ) @ 1A (typ. 5V out).

**Ground Pin Current:** 55 μA (typ) at full load. **Adjust Pin Voltage:** 2.5% (25°C) accuracy.

### Features

- Output voltage range of 1.25V 9V

- 2.5% adjust pin voltage accuracy (25°C)

- Low dropout voltage: 450mV @ 1A (typ, 5V out)

- Wide input voltage range (2.7V to 10V)

- Precision (trimmed) bandgap reference

- Guaranteed specs for -40°C to +125°C

- 1µA off-state quiescent current

- Thermal overload protection

- Foldback current limiting

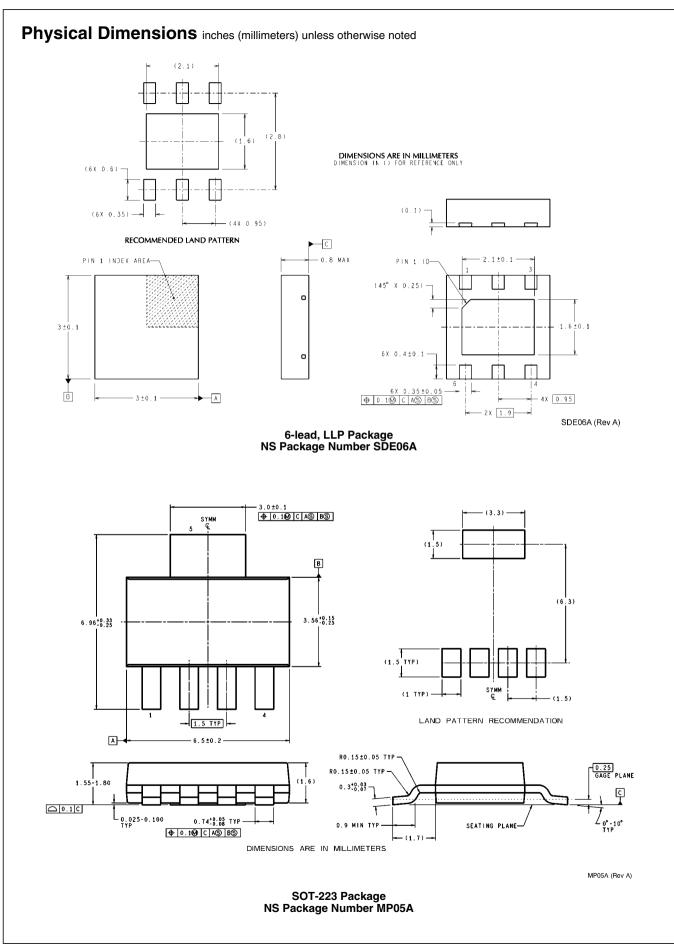

- SOT-223 and 6-Lead LLP packages

- Enable pin (LP38692-ADJ)

### Applications

- Hard Disk Drives

- Notebook Computers

- Battery Powered Devices

- Portable Instrumentation

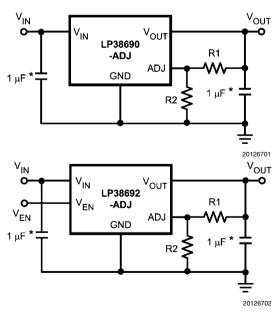

### **Typical Application Circuits**

$V_{OUT} = V_{ADJ} x (1 + R1/R2)$

Note: \*Minimum value required for stability.

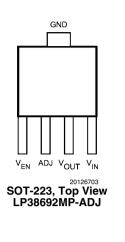

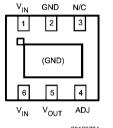

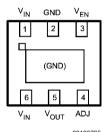

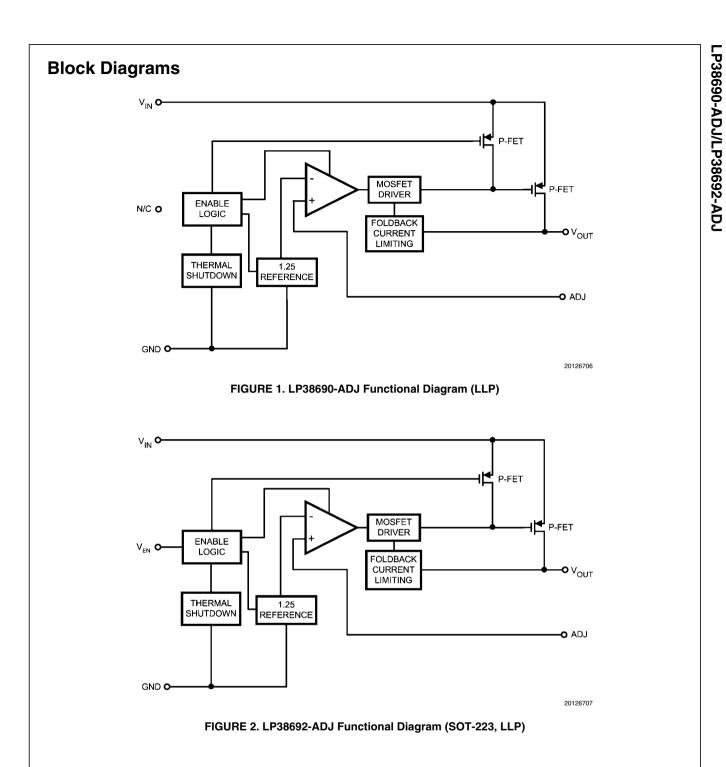

### **Connection Diagrams**

6-Lead LLP, Bottom View LP38690SD-ADJ

6-Lead LLP, Bottom View LP38692SD-ADJ

### **Pin Description**

| PIN              | DESCRIPTION                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IN</sub>  | This is the input supply voltage to the regulator. For LLP package devices, both V <sub>IN</sub> pins must be tied                                 |

|                  | together for full current operation (500mA maximum per pin).                                                                                       |

| GND              | Circuit ground for the regulator. This is connected to the die through the lead frame, and also functions                                          |

|                  | as the heat sink when the large ground pad is soldered down to a copper plane.                                                                     |

| V <sub>OUT</sub> | Regulated output voltage.                                                                                                                          |

| V <sub>EN</sub>  | The enable pin allows the part to be turned ON and OFF by pulling this pin high or low.                                                            |

| ADJ              | The adjust pin is used to set the regulated output voltage by connecting it to the external resistors R1 and R2 (see Typical Application Circuit). |

### **Ordering Information**

| Order Number   | Package Marking | Package Type | Package Drawing | Supplied As              |

|----------------|-----------------|--------------|-----------------|--------------------------|

| LP38690SD-ADJ  | L112B           | 6-Lead LLP   | SDE06A          | 1000 Units Tape and Reel |

| LP38692SD-ADJ  | L122B           | 6-Lead LLP   | SDE06A          | 1000 Units Tape and Reel |

| LP38692MP-ADJ  | LJNB            | SOT-223      | MP05A           | 1000 Units Tape and Reel |

| LP38690SDX-ADJ | L112B           | 6-Lead LLP   | SDE06A          | 4500 Units Tape and Reel |

| LP38692SDX-ADJ | L122B           | 6-Lead LLP   | SDE06A          | 4500 Units Tape and Reel |

| LP38692MPX-ADJ | LJNB            | SOT-223      | MP05A           | 2000 Units Tape and Reel |

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Storage Temperature Range         | –65°C to +150°C    |

|-----------------------------------|--------------------|

| Lead Temp. (Soldering, 5 seconds) | 260°C              |

| ESD Rating (Note 3)               | 2 kV               |

| Power Dissipation (Note 2)        | Internally Limited |

V(max) All pins (with respect to GND) I<sub>OUT</sub>

Junction Temperature

## **Operating Ratings**

V<sub>IN</sub> Supply Voltage 0 Т

2.7V to 10V

-0.3V to 12V

Internally Limited

-40°C to +150°C

| Dperating Junction                                                                 | -40°C to +125°C                                                               |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| e are for $T_J = 25^{\circ}C$ , and limit $V_{OUT} + 1V$ , $C_{IN} = C_{OUT} = 10$ | s in <b>boldface type</b> apply over<br>μF, I <sub>LOAD</sub> = 10mA. Min/Max |

Electrical Characteristics Limits in standard typeface the full operating temperature range. Unless otherwise specified:  $V_{IN}$  = limits are guaranteed through testing, statistical correlation, or design.

| Symbol                            | Parameter                                                                                | Conditions                                                 | Min   | Typ<br>(Note 4) | Мах         | Units |

|-----------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------|-------|-----------------|-------------|-------|

|                                   |                                                                                          | V <sub>IN</sub> = 2.7V                                     | 1.219 | 1.25            | 1.281       |       |

| V <sub>ADJ</sub>                  | ADJ Pin Voltage                                                                          | $3.2V \le V_{IN} \le 10V$<br>100 µA < I <sub>L</sub> < 1A  | 1.187 | 1.25            | 1.313       | V     |

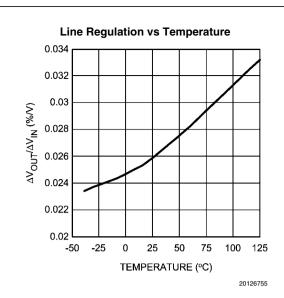

| ΔV <sub>O</sub> /ΔV <sub>IN</sub> | Output Voltage Line Regulation $V_{O} + 0.5V \le V_{IN} \le 10V$ (Note 6) $I_{L} = 25mA$ |                                                            |       | 0.03            | 0.1         | %/V   |

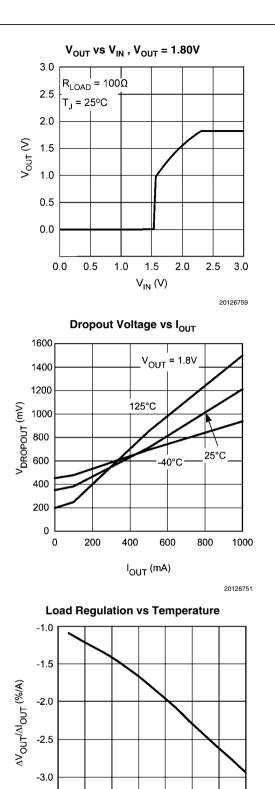

| ΔV <sub>O</sub> /ΔI <sub>L</sub>  | Output Voltage Load Regulation<br>(Note 7)                                               | $1 \text{ mA} < I_{L} < 1A$ $V_{IN} = V_{O} + 1V$          |       | 1.8             | 5           | %/A   |

|                                   |                                                                                          | (V <sub>O</sub> = 1.8V)<br>I <sub>L</sub> = 1A             |       | 950             | 1600        |       |

| V <sub>IN</sub> - V <sub>O</sub>  | Dropout Voltage (Note 8)                                                                 | $(V_{O} = 2.5V)$ $I_{L} = 0.1A$ $I_{L} = 1A$               |       | 80<br>800       | 145<br>1300 | mV    |

|                                   |                                                                                          |                                                            |       | 65<br>650       | 110<br>1000 |       |

|                                   |                                                                                          | $(V_{O} = 5V)$ $I_{L} = 0.1A$ $I_{L} = 1A$                 |       | 45<br>450       | 100<br>800  |       |

| Ι <sub>Q</sub>                    | Quiescent Current                                                                        | V <sub>IN</sub> ≤ 10V, I <sub>L</sub> = 100 µA - 1A        |       | 55              | 100         |       |

|                                   |                                                                                          | V <sub>EN</sub> ≤ 0.4V, (LP38692-ADJ Only)                 |       | 0.001           | 1           | μA    |

| I <sub>L</sub> (MIN)              | Minimum Load Current                                                                     | $V_{\rm IN} - V_{\rm O} \le 4V$                            |       |                 | 100         |       |

| I <sub>FB</sub>                   | Foldback Current Limit                                                                   | $V_{\rm IN} - V_{\rm O} > 5V$                              |       | 450             |             |       |

|                                   |                                                                                          | $V_{\rm IN} - V_{\rm O} < 4V$                              |       | 1500            |             | mA    |

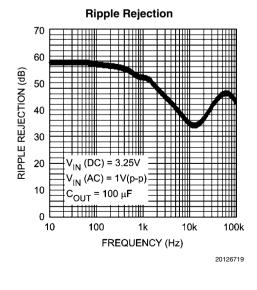

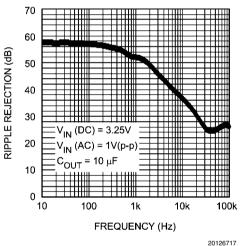

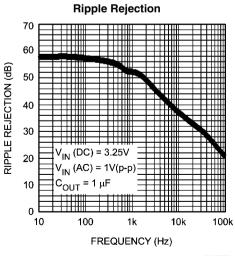

| PSRR                              | Ripple Rejection                                                                         | $V_{IN} = V_O + 2V(DC)$ , with $1V(p-p) / 120Hz$<br>Ripple |       | 55              |             | dB    |

| T <sub>SD</sub>                   | Thermal Shutdown Activation<br>(Junction Temp)                                           | 160                                                        |       |                 | °C          |       |

| T <sub>SD</sub> (HYST)            | Thermal Shutdown Hysteresis<br>(Junction Temp)                                           |                                                            |       | 10              |             |       |

| I <sub>ADJ</sub>                  | ADJ Input Leakage Current                                                                | V <sub>ADJ</sub> = 0 - 1.5V<br>V <sub>IN</sub> = 10V       | -100  | 0.01            | 100         | nA    |

| Ó                                       |

|-----------------------------------------|

|                                         |

| ◄                                       |

| 1                                       |

| N                                       |

| റ                                       |

| G                                       |

| õ                                       |

| õ                                       |

| ò                                       |

| -                                       |

| _                                       |

| -                                       |

| ر                                       |

|                                         |

| 1                                       |

| -                                       |

| Ġ                                       |

| ×                                       |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

| Q                                       |

| æ                                       |

| ന                                       |

| Δ.                                      |

|                                         |

|                                         |

| Symbol                | Parameter                                 | Conditions                                             | Min | Typ<br>(Note 4) | Мах | Units  |

|-----------------------|-------------------------------------------|--------------------------------------------------------|-----|-----------------|-----|--------|

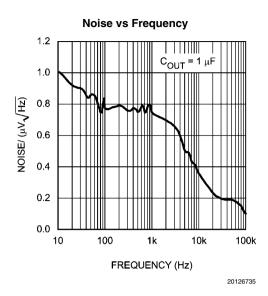

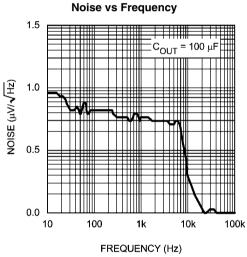

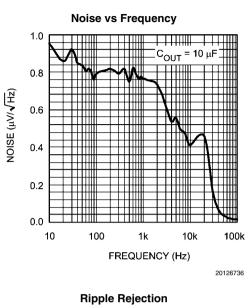

| e <sub>n</sub>        | Output Noise                              | BW = 10Hz to 10kHz<br>$V_0 = 3.3V$                     |     | 0.7             |     | µV/√Hz |

| V <sub>O</sub> (LEAK) | Output Leakage Current                    | $V_{\rm O} = V_{\rm O}({\rm NOM}) + 1V @ 10V_{\rm IN}$ |     | 0.5             | 2   | μA     |

| V <sub>EN</sub>       | Enable Voltage (LP38692-ADJ               | Output = OFF                                           |     |                 | 0.4 |        |

|                       | Only)                                     | Output = ON, $V_{IN} = 4V$                             | 1.8 |                 |     | v      |

|                       |                                           | Output = ON, $V_{IN} = 6V$                             | 3.0 |                 |     | ]      |

|                       |                                           | Output = ON, V <sub>IN</sub> = 10V                     | 4.0 |                 |     |        |

| I <sub>EN</sub>       | Enable Pin Leakage (LP38692-<br>ADJ Only) | V <sub>EN</sub> = 0V or 10V, V <sub>IN</sub> = 10V     | -1  | 0.001           | 1   | μA     |

Note 1: Absolute maximum ratings indicate limits beyond which damage to the component may occur. Operating ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications, see Electrical Characteristics. Specifications do not apply when operating the device outside of its rated operating conditions.

**Note 2:** At elevated temperatures, device power dissipation must be derated based on package thermal resistance and heatsink values (if a heatsink is used). The junction-to-ambient thermal resistance ( $\theta_{J,A}$ ) for the SOT-223 is approximately 125 °C/W for a PC board mounting with the device soldered down to minimum copper area (less than 0.1 square inch). If one square inch of copper is used as a heat dissipator for the SOT-223, the  $\theta_{J,A}$  drops to approximately 70 °C/W. The  $\theta_{J,A}$  values for the LLP package are also dependent on trace area, copper thickness, and the number of thermal vias used (refer to application note AN-1187). If power disspation causes the junction temperature to exceed specified limits, the device will go into thermal shutdown.

Note 3: ESD is tested using the human body model which is a 100pF capacitor discharged through a 1.5k resistor into each pin.

Note 4: Typical numbers represent the most likely parametric norm for 25°C operation.

Note 5: If used in a dual-supply system where the regulator load is returned to a negative supply, the output pin must be diode clamped to ground.

Note 6: Output voltage line regulation is defined as the change in output voltage from nominal value resulting from a change in input voltage.

Note 7: Output voltage load regulation is defined as the change in output voltage from nominal value as the load current increases from 1mA to full load.

Note 8: Dropout voltage is defined as the minimum input to output differential required to maintain the output within 100mV of nominal value.

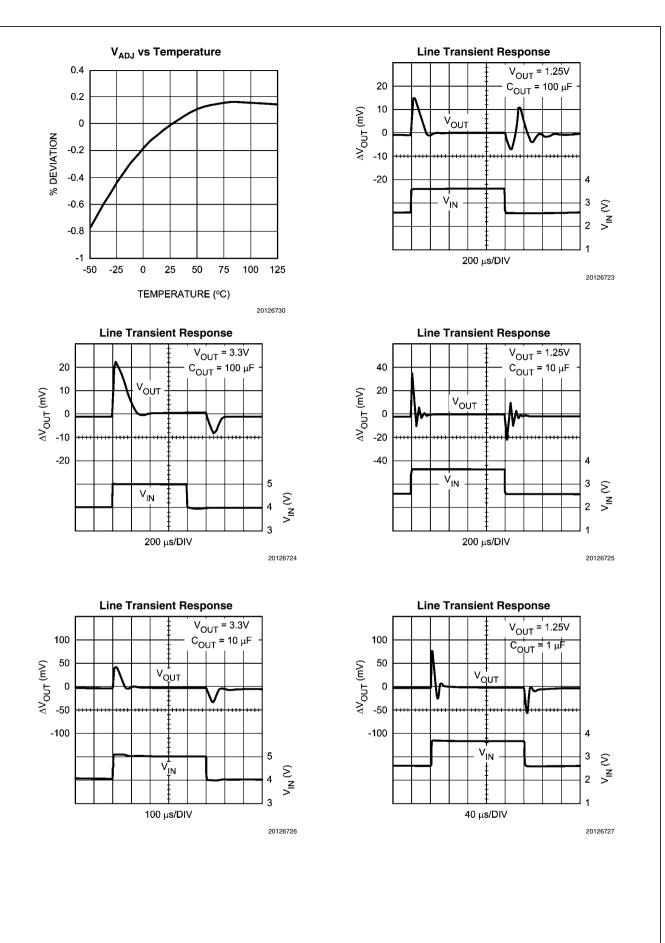

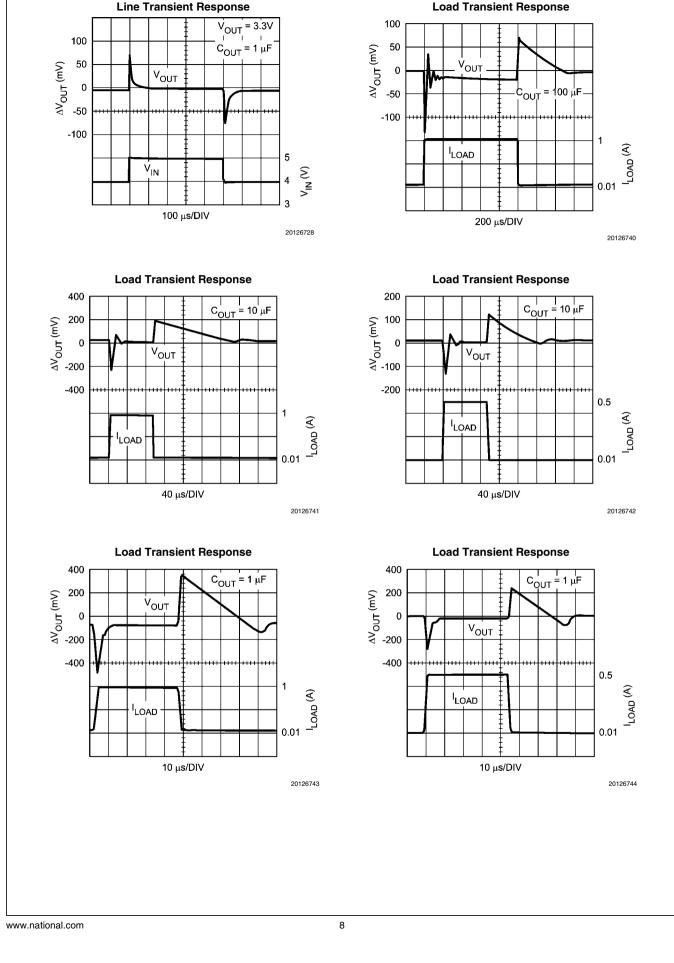

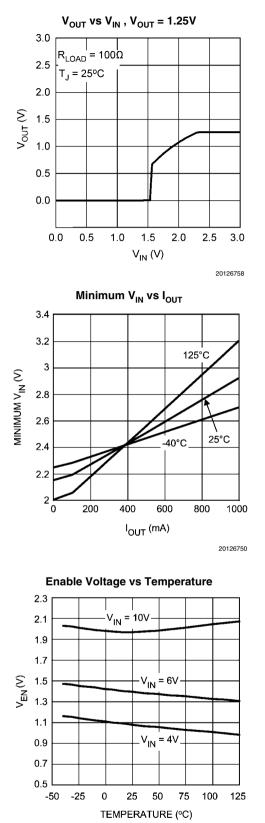

**Typical Performance Characteristics** Unless otherwise specified:  $T_J = 25^{\circ}C$ ,  $C_{IN} = C_{OUT} = 10 \,\mu$ F, enable pin is tied to  $V_{IN}$  (LP38692-ADJ only),  $V_O = 1.25V$ ,  $V_{IN} = 2.7V$ ,  $I_L = 10$ mA.

20126721

20126737

20126753

-3.5

-50

-25

0

25 50

TEMPERATURE (°C)

75

100

20126754

### **Application Hints**

#### EXTERNAL CAPACITORS

Like any low-dropout regulator, external capacitors are required to assure stability. These capacitors must be correctly selected for proper performance.

**INPUT CAPACITOR:** An input capacitor of at least  $1\mu$ F is required (ceramic recommended). The capacitor must be located not more than one centimeter from the input pin and returned to a clean analog ground.

**OUTPUT CAPACITOR:** An output capacitor is required for loop stability. It must be located less than 1 centimeter from the device and connected directly to the output and ground pins using traces which have no other currents flowing through them.

The minimum amount of output capacitance that can be used for stable operation is  $1\mu$ F. Ceramic capacitors are recommended (the LP38690/2-ADJ was designed for use with ultra low ESR capacitors). The LP38690/2-ADJ is stable with any output capacitor ESR between zero and 100 Ohms.

**SETTING THE OUTPUT VOLTAGE:** The output voltage is set using the external resistors R1 and R2 (see Typical Application Circuit). The output voltage will be given by the equation:

$$V_{OUT} = V_{ADJ} X (1 + R1/R2)$$

Because the part has a minimum load current requirement of 100  $\mu$ A, it is recommended that R2 always be 12k Ohms or less to provide adequate loading. Even if a minimum load is always provided by other means, it is not recommended that very high value resistors be used for R1 and R2 because it can make the ADJ node susceptible to noise pickup. A maximum value of 100k is recommended for R2 to prevent this from occurring.

**ENABLE PIN (LP38692-ADJ only):** The LP38692-ADJ has an enable pin which turns the regulator output on and off. Pulling the enable pin down to a logic low will turn the part off. The voltage the pin has to be pulled up to in order to assure the part is on depends on input voltage (refer to Electrical Characteristics section). This pin should be tied to  $V_{\rm IN}$  if the enable function is not used.

**FOLDBACK CURRENT LIMITING:** Foldback current limiting is built into the LP38690/2-ADJ which reduces the amount of output current the part can deliver as the output voltage is reduced. The amount of load current is dependent on the differential voltage between  $V_{IN}$  and  $V_{OUT}$ . Typically, when this differential voltage exceeds 5V, the load current will limit at about 450 mA. When the  $V_{IN} - V_{OUT}$  differential is reduced below 4V, load current is limited to about 1500 mA.

#### SELECTING A CAPACITOR

It is important to note that capacitance tolerance and variation with temperature must be taken into consideration when selecting a capacitor so that the minimum required amount of capacitance is provided over the full operating temperature range.

#### **Capacitor Characteristics**

**CERAMIC:** For values of capacitance in the 10 to 100  $\mu$ F range, ceramics are usually larger and more costly than tantalums but give superior AC performance for bypassing high frequency noise because of very low ESR (typically less than 10 m $\Omega$ ). However, some dielectric types do not have good capacitance characteristics as a function of voltage and temperature.

Z5U and Y5V dielectric ceramics have capacitance that drops severely with applied voltage. A typical Z5U or Y5V capacitor can lose 60% of its rated capacitance with half of the rated voltage applied to it. The Z5U and Y5V also exhibit a severe temperature effect, losing more than 50% of nominal capacitance at high and low limits of the temperature range.

X7R and X5R dielectric ceramic capacitors are strongly recommended if ceramics are used, as they typically maintain a capacitance range within  $\pm 20\%$  of nominal over full operating ratings of temperature and voltage. Of course, they are typically larger and more costly than Z5U/Y5U types for a given voltage and capacitance.

**TANTALUM:** Solid Tantalum capacitors have good temperature stability: a high quality Tantalum will typically show a capacitance value that varies less than 10-15% across the full temperature range of -40°C to 125°C. ESR will vary only about 2X going from the high to low temperature limits.

The increasing ESR at lower temperatures can cause oscillations when marginal quality capacitors are used (if the ESR of the capacitor is near the upper limit of the stability range at room temperature).

### PCB LAYOUT

Good PC layout practices must be used or instability can be induced because of ground loops and voltage drops. The input and output capacitors must be directly connected to the input, output, and ground pins of the regulator using traces which do not have other currents flowing in them (Kelvin connect).

The best way to do this is to lay out  $C_{IN}$  and  $C_{OUT}$  near the device with short traces to the  $V_{IN}$ ,  $V_{OUT}$ , and ground pins. The regulator ground pin should be connected to the external circuit ground so that the regulator and its capacitors have a "single point ground".

It should be noted that stability problems have been seen in applications where "vias" to an internal ground plane were used at the ground points of the IC and the input and output capacitors. This was caused by varying ground potentials at these nodes resulting from current flowing through the ground plane. Using a single point ground technique for the regulator and it's capacitors fixed the problem. Since high current flows through the traces going into V<sub>IN</sub> and coming from V<sub>OUT</sub>. Kelvin connect the capacitor leads to these pins so there is no voltage drop in series with the input and output capacitors.

### **RFI/EMI SUSCEPTIBILITY**

RFI (radio frequency interference) and EMI (electromagnetic interference) can degrade any integrated circuit's performance because of the small dimensions of the geometries inside the device. In applications where circuit sources are present which generate signals with significant high frequency energy content (> 1 MHz), care must be taken to ensure that this does not affect the IC regulator.

If RFI/EMI noise is present on the input side of the regulator (such as applications where the input source comes from the output of a switching regulator), good ceramic bypass capacitors must be used at the input pin of the IC.

If a load is connected to the IC output which switches at high speed (such as a clock), the high-frequency current pulses required by the load must be supplied by the capacitors on the IC output. Since the bandwidth of the regulator loop is less than 100 kHz, the control circuitry cannot respond to load changes above that frequency. This means the effective output impedance of the IC at frequencies above 100 kHz is determined only by the output capacitor(s). In applications where the load is switching at high speed, the output of the IC may need RF isolation from the load. It is recommended that some inductance be placed between the output capacitor and the load, and good RF bypass capacitors be placed directly across the load.

PCB layout is also critical in high noise environments, since RFI/EMI is easily radiated directly into PC traces. Noisy circuitry should be isolated from "clean" circuits where possible, and grounded through a separate path. At MHz frequencies, ground planes begin to look inductive and RFI/ EMI can cause ground bounce across the ground plane. In multi-layer PCB applications, care should be taken in layout so that noisy power and ground planes do not radiate directly into adjacent layers which carry analog power and ground.

#### OUTPUT NOISE

Noise is specified in two ways- **Spot Noise** or **Output Noise** density is the RMS sum of all noise sources, measured at the regulator output, at a specific frequency (measured with a 1Hz bandwidth). This type of noise is usually plotted on a curve as a function of frequency. **Total Output Noise** or **Broad-Band Noise** is the RMS sum of spot noise over a specified bandwidth, usually several decades of frequencies. Attention should be paid to the units of measurement. Spot noise is measured in units  $\mu$ V/root-Hz or nV/root-Hz and total output noise is measured in  $\mu$ V(rms)

The primary source of noise in low-dropout regulators is the internal reference. Noise can be reduced in two ways: by increasing the transistor area or by increasing the current drawn by the internal reference. Increasing the area will decrease the chance of fitting the die into a smaller package. Increasing the current drawn by the internal reference increases the total supply current (ground pin current).

LP38690-ADJ/LP38692-ADJ

# Notes

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com